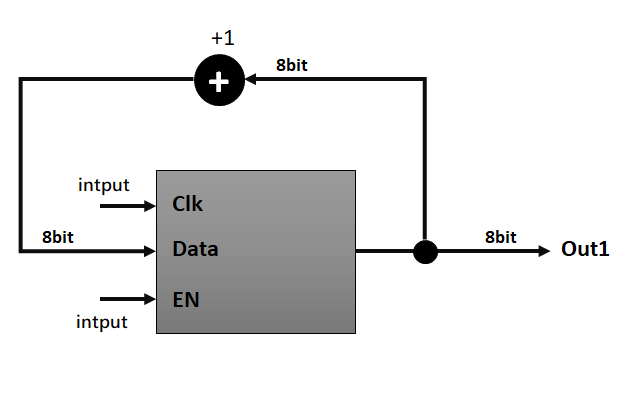

我們的第一個電路已經講完了

第一個電路:

再到下一個電路之前,我想先講講 case

在簡單的架構中 reg 就需要 reset

一旦跳出 reset之後 簡單的例子中,滿常都會看到 case來處理

always@(negedge reset1 or posedge clk)

begin

if( ~reset1) begin

end

else begin

case (條件設定)

條件1:

敘述執行方式1

條件2:

敘述執行方式2

.

.

.

.

.

default:

默認執行

endcase

end

end

endmodule

昨天的程式碼改成 數到 5 就歸零

我們就繼續看昨天的執行碼

我們改成數到 5 就歸零在執行

module Clk_Add1(reset1,clk,Out1);

input reset1 ,clk;

output[7:0] Out1;

reg[7:0] Out1;

wire[7:0] Date;

assign Date = Out1+1;

always@(negedge reset1 or posedge clk)

begin

if( ~reset1) begin

Out1<=0;

end

else begin

case (Out1<5)

1:

Out1<=Date;

0:

Out1<=0;

default:

Out1<=0;

endcase

end

end

endmodule

中間其實就是多了一項

case (Out1<5)

1:

Out1<=Date;

0:

Out1<=0;

default:

Out1<=0;

endcase

tb

tb大概寫一下

module tb1();

reg reset1 ,clk;

wire[7:0] Out1;

Clk_Add1 test(

.reset1(reset1),

.clk(clk),

.Out1(Out1)

);

initial begin

reset1 <= 0 ;

clk <= 0 ;

# 20;

reset1 <= 1 ;

# 5000;

$stop;

end

always #10 clk<=~clk;

endmodule

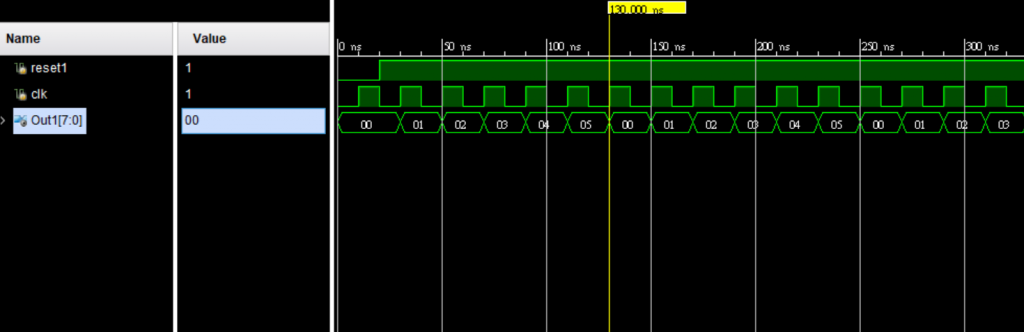

執行看看,到5的時候就歸零

這時來問個問題

如果我 case改的 將 <= 變成 = 會怎樣呢??

case (Out1<5)

1:

Out1 =Date;

0:

Out1 =0;

default:

Out1<=0;

endcase